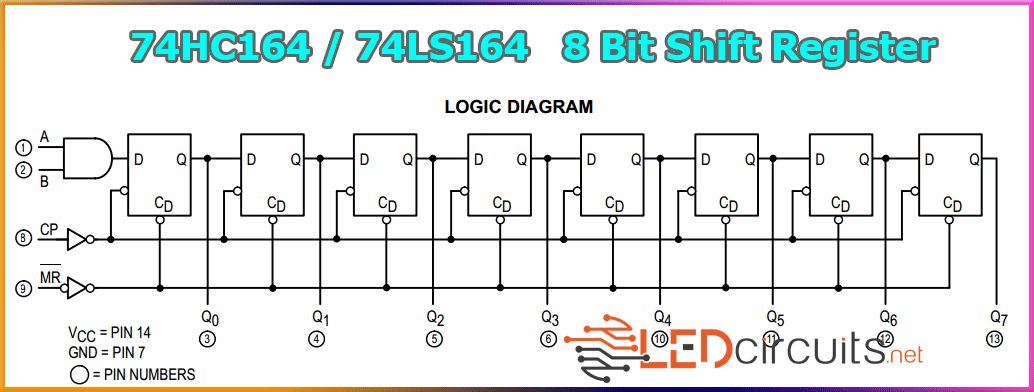

74HC164 is an 8-bit Serial input Parallel output (SIPO) shift register. In the serial input port, there is an AND gate as seen in the logic diagram. Also MR input to clear the output port whenever you want.

The 74HC164 can operate in the 2-6V and you can get 4 mA current through each channel under 5V.

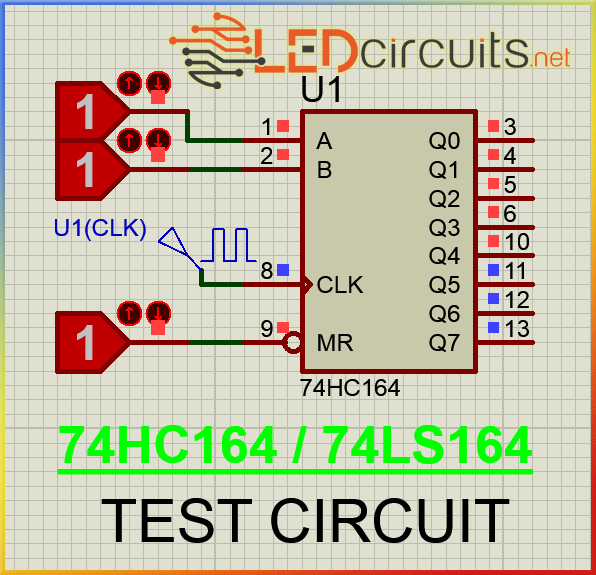

Unlike other shift registers, the data inputs A and B are connected to the AND logic gate. For this reason, if A and B inputs are Logic 1, data = 1, if any of A or B inputs is Logic 0, data = 0.

In the application, we keep the B input at logic 1 level and make the data input from the A input.

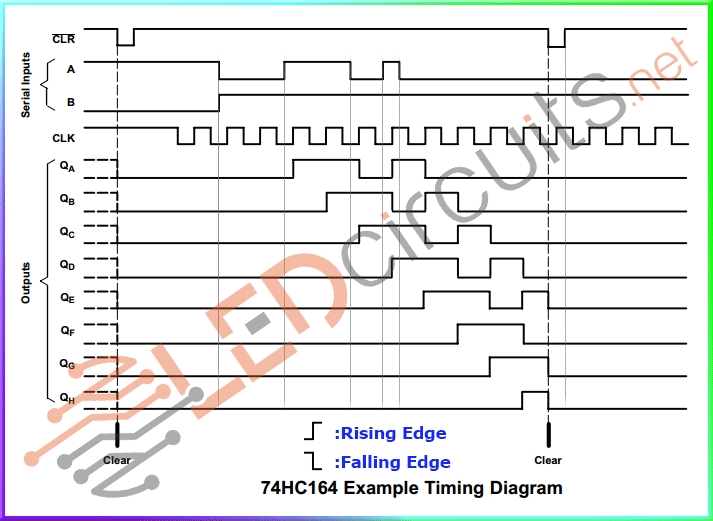

- Another issue, you should pay attention to is the relationship between the clock pulses and the output port.

As seen in the timing diagram, the 74HC164 / 74LS164 is triggered when clock signal change to rising edge (low to high). Scrolling continues as you apply the clock pulses.

It is enough to make MR (Master Reset) pin logic 0 to clear the output port.

Nice Post

Thank you